Explain the working of the instruction pipelining, with the help of a diagram 5m Dec2005

INSTRUCTION PIPELINING

To extract better performance instruction execution can be done through instruction pipeline. The instruction pipelining involves decomposing of an instruction execution to a number of pipeline stages.

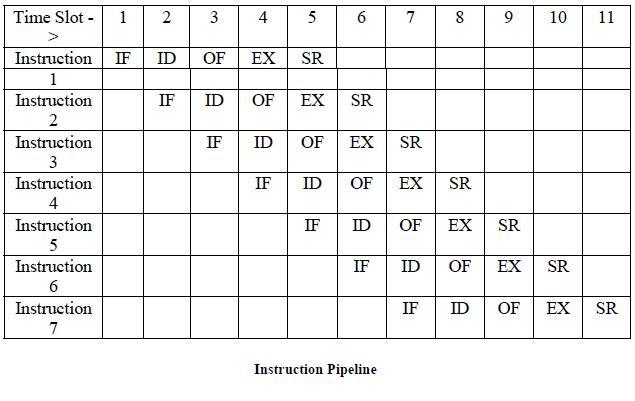

Some of the common pipeline stages can be instruction fetch (IF), instruction decode (ID), operand fetch (OF), execute (EX), store results (SR).

An instruction pipe may involve any combination of such stages. A major design decision here is that the instruction stages should be of equal execution time. The reason why it should be is,

A pipeline allows overlapped execution of instructions. Thus, during the course of execution of an instruction the following may be a scenario of execution.

A pipeline allows overlapped execution of instructions. Thus, during the course of execution of an instruction the following may be a scenario of execution.

Please note the following observations about the above figure:

- The pipeline stages are like steps. Thus, a step of the pipeline is to be complete in a time slot. The size of the time slot will be governed by the stage taking maximum time. Thus, if the time taken in various stages is almost similar, we get the best results.

- The first instruction execution is completed on completion of 5th time slot, but afterwards, in each time slot the next instruction gets executed. So, in ideal conditions one instruction is executed in the pipeline in each time slot.

- After the 5th time slot and afterwards the pipe is full. In the 5th time slot the stages of execution of five instructions are:

SR (instruction 1) (Requires memory reference)

EX (instruction 2) (No memory reference)

OF (instruction 3) (Requires memory reference)

ID (instruction 4) (No memory reference)

IF (instruction 5) (Requires memory reference)