MASTER OF COMPUTER APPLICATIONS

Course Code : MCS-012

Course Title : Computer Organisation and Assembly Language Programming

Assignment Number : MCA(I)/012/Assignment/15-16

Maximum Marks : 100

Weightage : 25%

Assume that the machine as stated in part (a) has named 5 of its general purpose registers based on their possible role in instruction execution as Program Counter (PC), Accumulator (AC), Memory Address Register (MAR), Instruction Register (IR) , Data Register (DR) and Flag registers (FR). To execute an instruction of the machine that has a direct memory operand and a register operand, the memory operand is first brought into the DR register and the register operand is transferred to AC register. The result of the operation is stored in the AC register. One of the instructions of the machine is given below:

ADD R1, X // this instruction adds the operand stored in

Register R1 and memory location X. The result is stored in the AC register.

Write and explain the sequence of micro-operations that are required to fetch and execute this instruction. Make and state suitable assumptions, if any.

STORE memAddress // this instruction result in storage of the content of AC register into the memory location specified by memAddress.

Write and explain the sequence of micro-operations that are required to fetch and execute this instruction Make and state suitable assumptions, if any.

The instruction execution using the micro-operations requires:

- Instruction fetch: fetching the instruction from the memory.

- Instruction decode: decode the instruction.

- Operand address calculation: find out the effective address of the operands.

- Execution: execute the instruction.

- Interrupt Acknowledge: perform an interrupt acknowledge cycle if an interrupt request is pending.

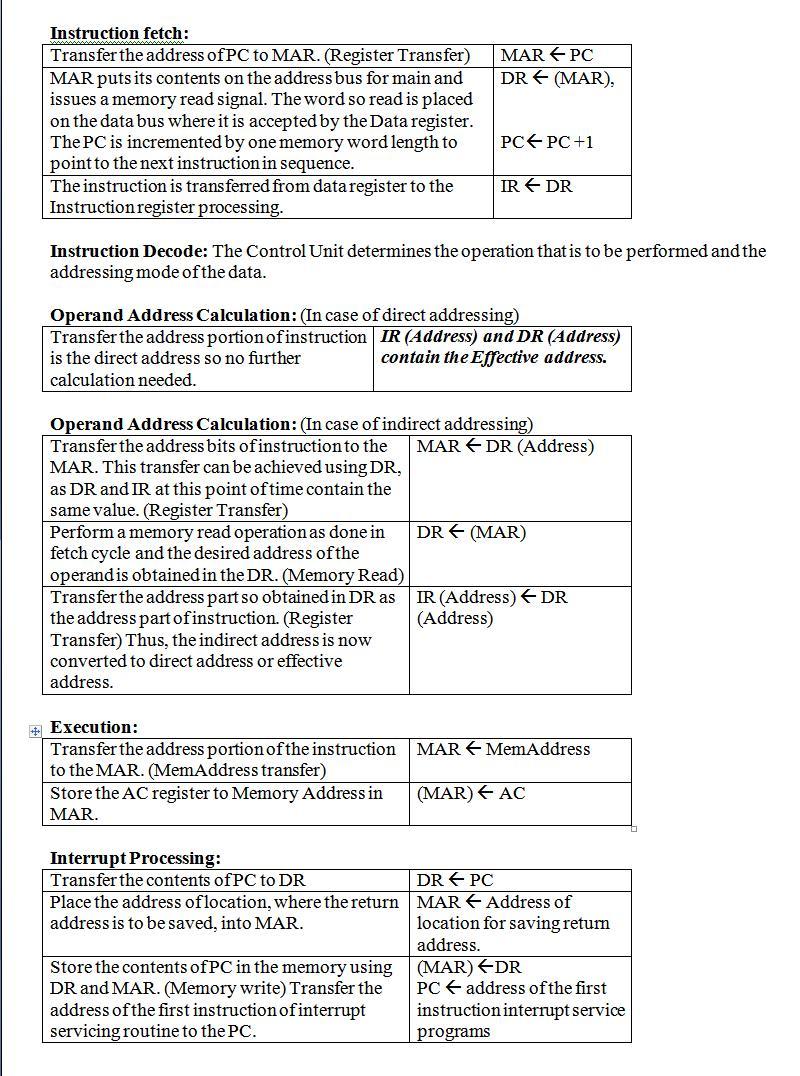

Instruction fetch:

Transfer the address of PC to MAR. (Register Transfer) MAR ß PC MAR puts its contents on the address bus for main and issues a memory read signal. The word so read is placed on the data bus where it is accepted by the Data register.The PC is incremented by one memory word length to point to the next instruction in sequence. DR ß (MAR), PCß PC +1

The instruction is transferred from data register to the Instruction register processing. IR ß DR Instruction Decode: The Control Unit determines the operation that is to be performed and the addressing mode of the data.

Operand Address Calculation: (In case of direct addressing)

Transfer the address portion of instruction is the direct address so no further calculation needed. IR (Address) and DR (Address) contain the Effective address. Operand Address Calculation: (In case of indirect addressing)

Transfer the address bits of instruction to the MAR. This transfer can be achieved using DR, as DR and IR at this point of time contain the same value. (Register Transfer) MAR ß DR (Address) Perform a memory read operation as done in fetch cycle and the desired address of the operand is obtained in the DR. (Memory Read) DR ß (MAR) Transfer the address part so obtained in DR as the address part of instruction. (Register Transfer) Thus, the indirect address is now converted to direct address or effective address. IR (Address) ß DR (Address) Execution:

Transfer the address portion of the instruction to the MAR. (MemAddress transfer) MAR ß MemAddress Store the AC register to Memory Address in MAR. (MAR) ß AC Interrupt Processing:

Transfer the contents of PC to DR DR ß PC Place the address of location, where the return address is to be saved, into MAR. MAR ß Address of location for saving return address. Store the contents of PC in the memory using DR and MAR. (Memory write) Transfer the address of the first instruction of interrupt servicing routine to the PC. (MAR) ßDRPC ß address of the first instruction interrupt service programs