Design and draw a master-slave flip flop using JK flipflops. What are the advantages it offers over other flip flops? 10m Jun2007

Master Slave Flip Flop

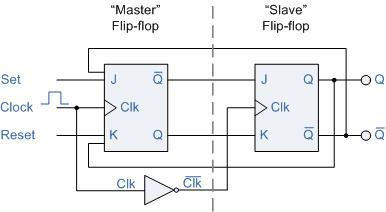

Master-slave flip flop consists of two flip-flops. One is the master flip-flop & other is called the slave flip-flop. The figure shows implementation of master-slave flipflop using J-K flip-flop.

Master Slave Flip Flop

From the above figure you can see that both the J-K flip flops are presented in a series connection. The output of the master J-K flip flop is fed to the input of the slave J-K flip flop. The output of the slave J-K flip flop is given as a feedback to the input of the master J-K flip flop. The clock pulse [Clk] is given to the master J-K flip flop and it is sent through a NOT Gate and thus inverted before passing it to the slave J-K flip flop.

Working

Now, let us summarize the working of this flip-flop:

(i) When the clock pulse is 0, the master flip-flop is disabled but the slave becomes active and it’s output Q & Q becomes equal to Y and Y respectively. Why? Well the possible combination of the value of Y and Y’ are either Y=1, Y =0 or Y=0 Y =1. Thus, the slave flip-flop can have following combinations: –

(a) J=1, K=0 which means Q=1, Q =0 (stet flip-flop)

(b) J=0, K=1 which means Q=0, Q =1 (clear flip-flop)

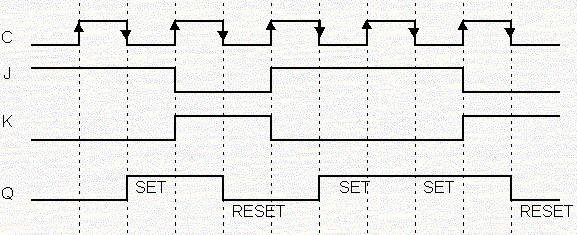

(ii) When Clk=1, the master J-K flip flop gets disabled. The Clk input of the master input will be the opposite of the slave input. So the master flip flop output will be recognized by the slave flip flop only when the Clk value becomes 0. Thus, when the clock pulse males a transition from 1 to 0, the locked outputs of the master flip flop are fed through to the inputs of the slave flip-flop making this flip flop edge or pulse-triggered. To understand better take a look at the timing diagram illustrated below.

Master Slave J-K Flip Flop Timing Diagram

Thus, the circuit accepts the value in the input when the clock is HIGH, and passes the data to the output on the falling-edge of the clock signal. This makes the Master-Slave J-K flip flop a Synchronous device as it only passes data with the timing of the clock signal.

Advantages of Master Slave J-K flip flop:

- The output timing is controlled differently.

- The master stage loads on one edge of the clock waveform and transfers to the slave on the other edge.

- With a basic edge-triggered type, the output changes with the same edge that latches the data in, the only delay is the internal propagation delay of the device.

- A lot of the time it makes no difference, but in some circuits you want the controlled delay on the Mater-Slave output.